# Systematic Approaches for Efficient and Scalable Deep Learning

Yuke Wang@Rice CS

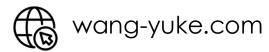

#### The Trend of DL Algorithm and Hardware

\* Recap of DL algorithms and hardware performance scaling.

Huge Potential with GPUs! But it still has a Large Gap!

#### Deep Learning Drives Computing Innovations

❖ Overview of my prior Ph.D. Research.

Model Design, Model Pruning (2018-19)

Hardware Accelerators (2020-21)

Runtime Systems, Compiler (2021-now)

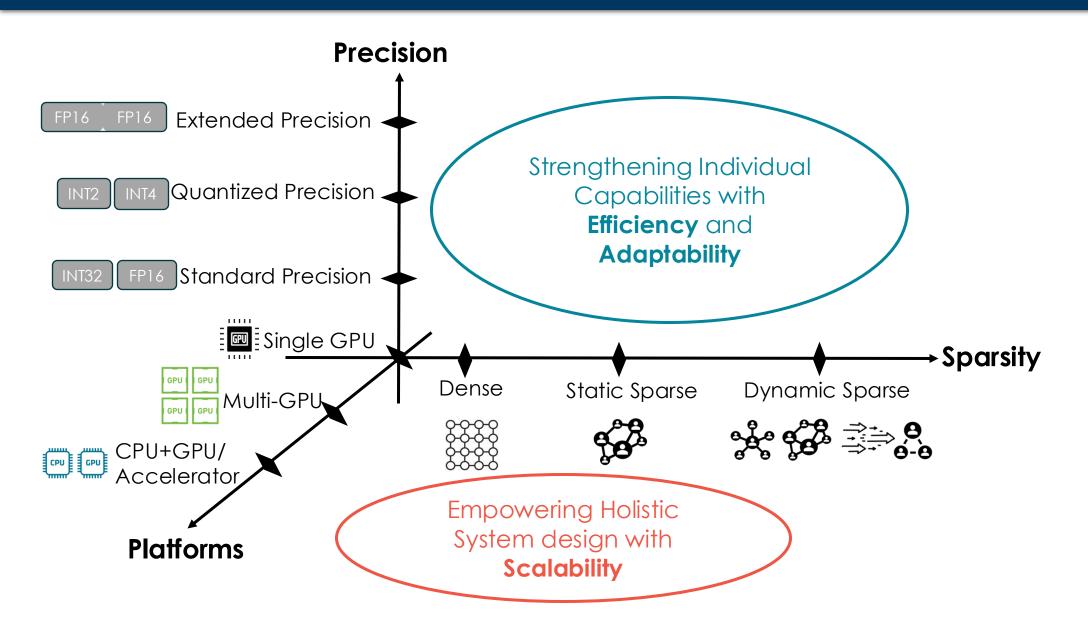

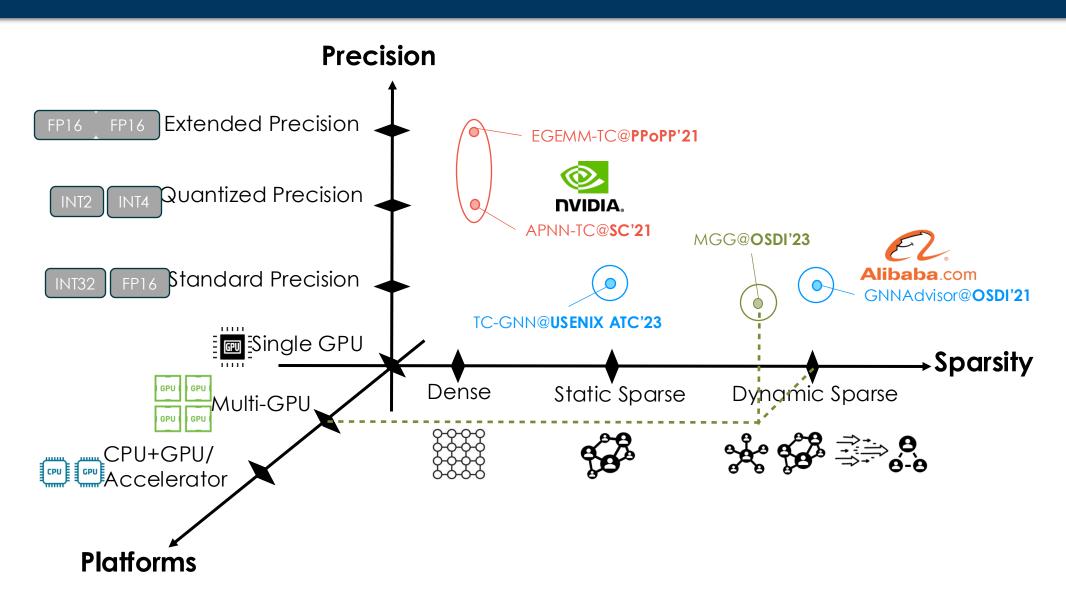

#### My Prior PhD Research Recap

#### My Prior Research Recap

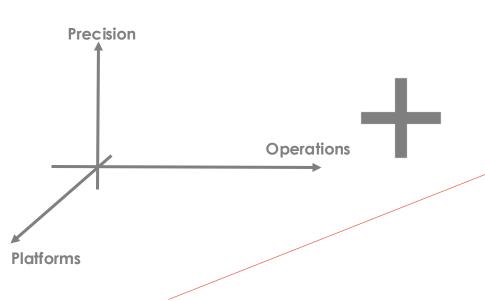

Precision

Sparsity

Scalability

#### Diverse Precision Demands for DL Applications

**Low-precision** quantized deep-learning applications.

| Quantized Deep Learning | Precision Requirements                                                                                                        |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| QNNs [JMLR' 18]         | <ul><li>1-bit Weight, 2-bit Activation for Vision Model,</li><li>3-bit Weight, 4-bit Activation for Language Model.</li></ul> |

| SGQuant [ICTAI'20]      | Graph Attention Model: <b>2-bit</b> Neighbor <b>Attention</b> , <b>4-bit</b> Neighbor <b>Aggregation</b> .                    |

| LLM.int8() [NeurIPS'22] | 8-bit Quantization for Transformers.                                                                                          |

|                         |                                                                                                                               |

Low-precision deep-learning applications **can** leverage low-precision GPU Tensor cores, but suffer from **low efficiency**.

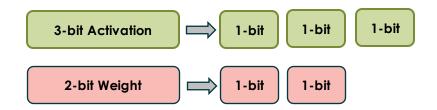

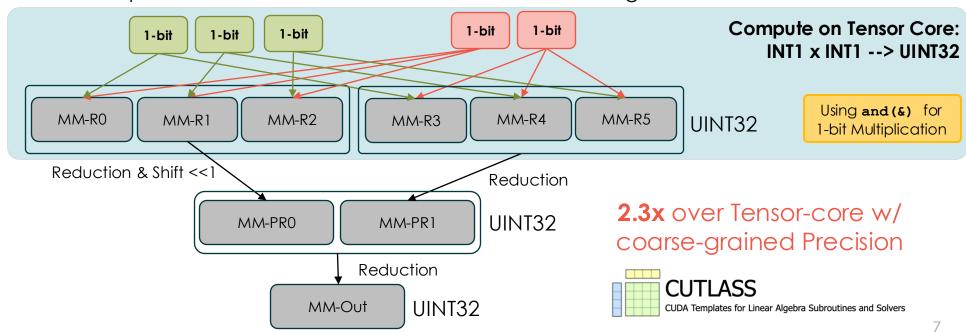

#### Bit Composition for Quantized Deep Learning [SC'21]

Insight: Quantized deep learning can be composed with the binary (1-bit) precision.

Example of 2-bit and 3-bit Precision in Quantized DNN Computing.

Multiplication between 3-bit Activation and 2-bit Weight

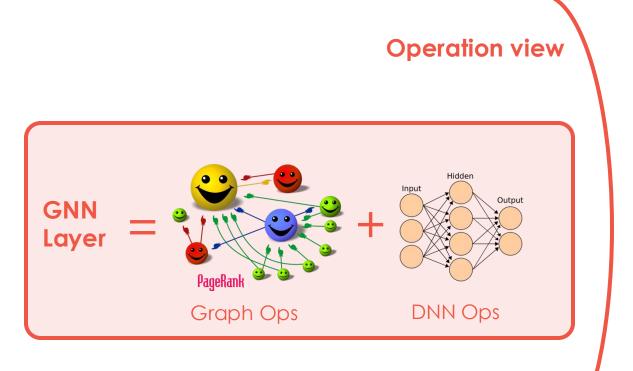

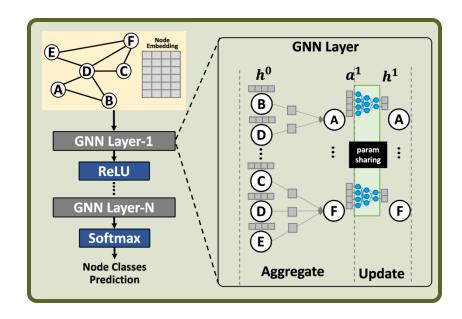

#### A Typical Paradigm of Graph Deep Learning

#### Model view

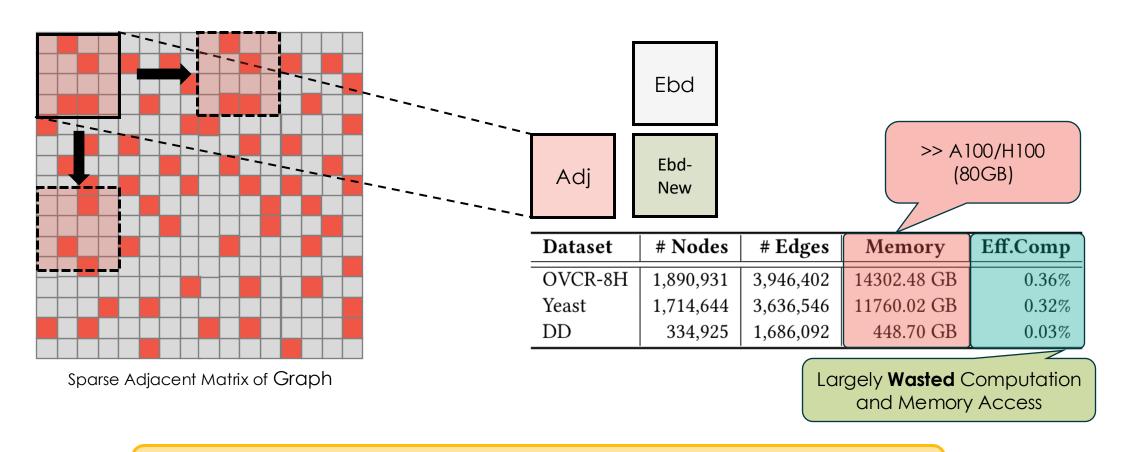

#### Challenge of Mapping Sparse Computing to Dense Units

Direct mapping suffers from extra high memory consumption and extremely low computing efficiency.

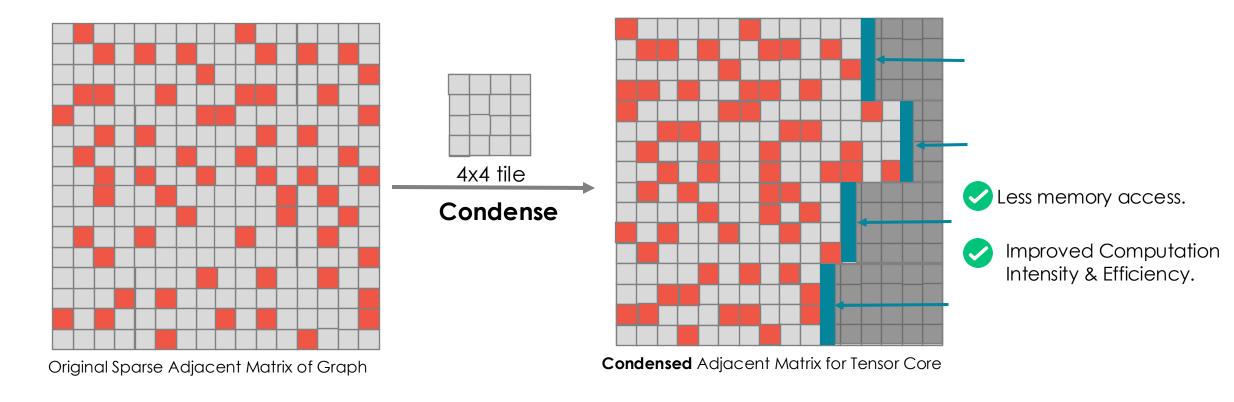

#### TC-GNN: Order-Invariant Transformation [ATC'23]

• Irregularly-scattered elements can be **condensed** to benefit high-performance dense GPU units.

1.50x ~ 6.70x over DGL operators (cuSPARSE).

Incorporated by SparseTIR in TVM Project.

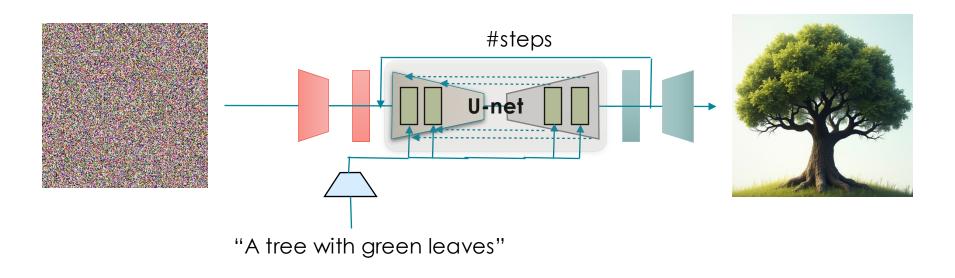

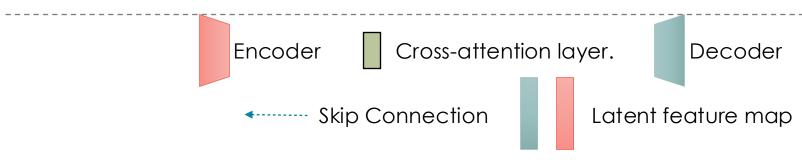

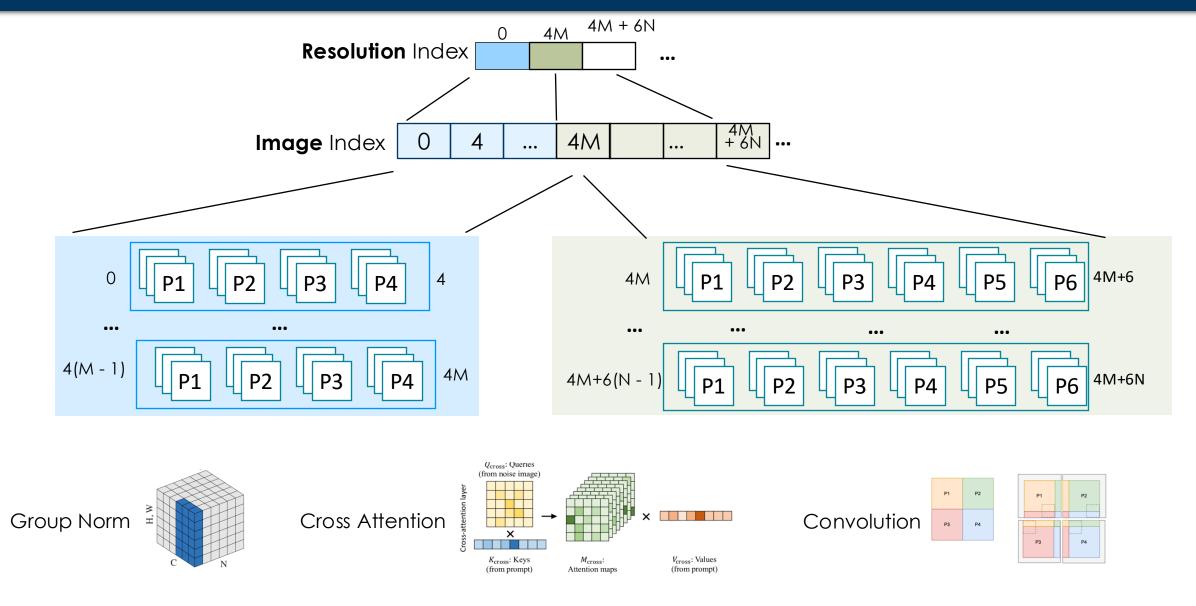

#### R1: Patch-based Stable Diffusion Serving

Architecture of Stable Diffusion Model.

#### R1: Patch-based Stable Diffusion Serving

#### R1: Patch-based Stable Diffusion Serving

#### R2: Efficient DLRM with CXL Disaggregated Memory

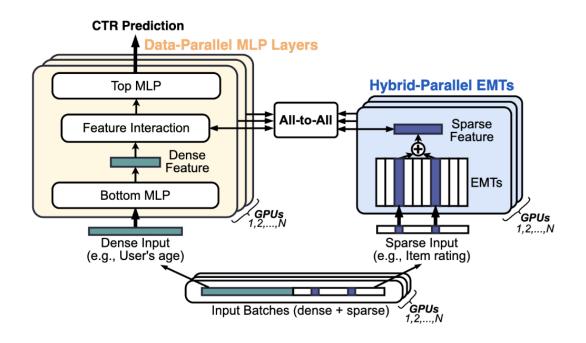

• Typical architecture and configuration of DLRMs.

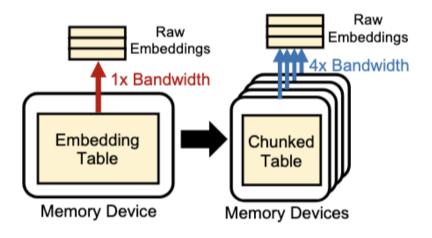

#### R2: Joint Optimization with Disaggregated Memory

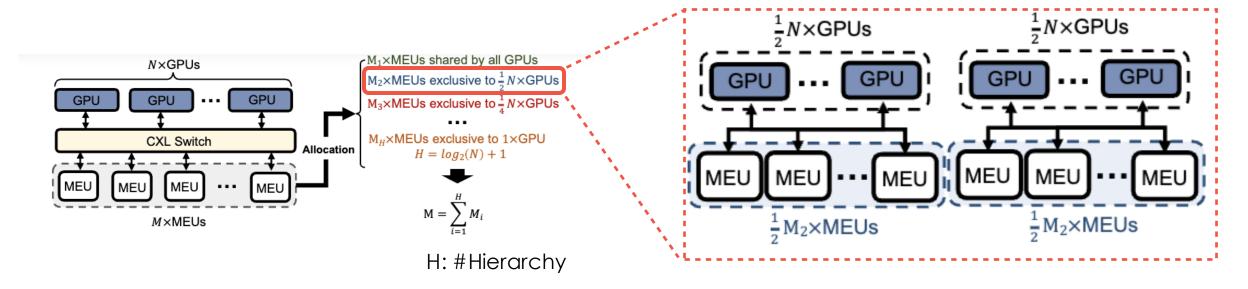

• Hierarchical memory layout with fine-grained access control enlarges design space.

#### R2: Joint Optimization with Disaggregated Memory

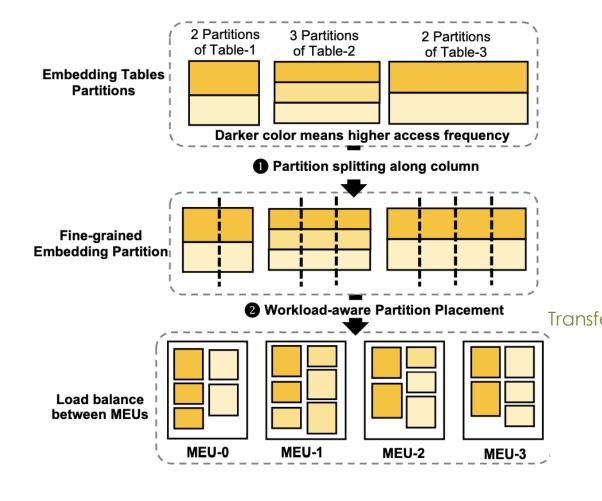

❖ Workload-aware Embedding Table Placement.

❖ ILP formulation for joint memory and table optimization.

Memory Unit Placement

$$\sum_{j=1}^{H} m_{ij} = 1, \ m_{ij} \in \{0, 1\}$$

Embedding Table Assignment

$$\sum_{j=0}^{H} t_{ij} = 1, \ t_{ij} \in \{0, 1\}$$

**H** is the number of memory hierarchy

Memory Constraints

$$Cap_j \leq Mem_j \quad j \in \{0, 1, \dots, H\}$$

$$Cap_{j} = \begin{cases} N * C_{G}, & j = 0 \\ \sum_{i=1}^{M} m_{ij} * C_{M} * \frac{1}{2^{j-1}}, & j \in \{1, 2, \dots, H\} \end{cases}$$

$$Mem_{j} = \sum_{i=1}^{T} t_{ij} * S_{i} * D_{i} * size(float) \quad j \in \{0, 1, \dots, H\}$$

Optimize & Lookup Efficiency

Transfer & Lookup  $minimize \ Max(L\_send_j + L\_lookup_j) \ j \in \{0, 1, \dots, H\}$

$$\begin{split} L\_send_{j} &= \begin{cases} 0, & j = 0 \\ \frac{B*size(float)*\sum_{i=1}^{K}D_{i}}{BW_{CXL}}, & j \in \{1, 2, \cdots, H\} \end{cases} \\ L\_lookup_{j} &= \frac{\sum_{i=1}^{T}t_{ij}*B*A_{i}*D_{i}*P_{i}*size(float)}{BW_{j}} \\ BW_{j} &= \begin{cases} BW_{GPU}, & j = 0 \\ Min(\sum_{i=1}^{M}m_{ij}*BW_{MEU}, & BW_{max}*2^{j-1}), \\ & j \in \{1, 2, \cdots, H\} \end{cases} \end{split}$$

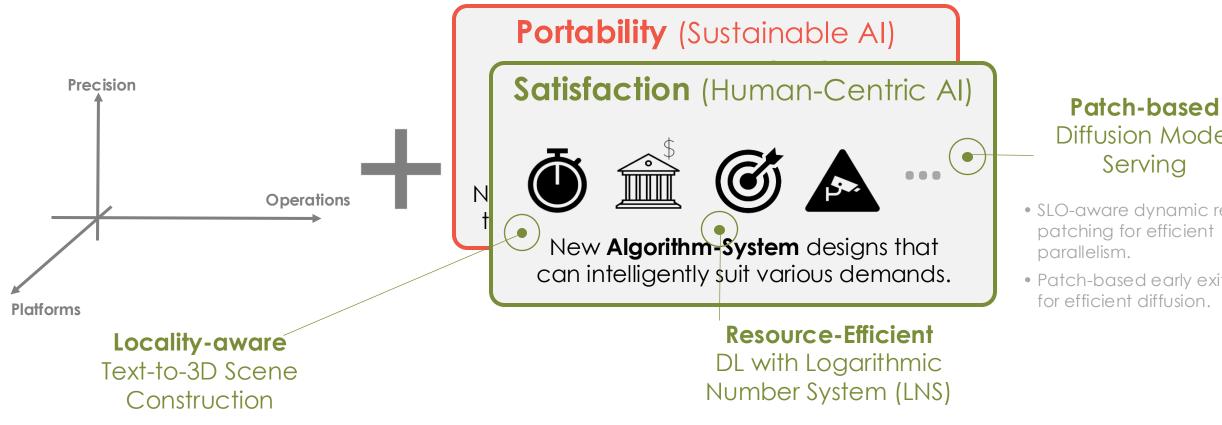

#### Future Research: New Hardware-System Optimization

#### Portability (Sustainable AI)

New **Hardware-System** Designs that adapt to diverse real-world application settings.

## Efficient DLRM with Disaggregated Memory (e.g., CXL)

- Co-design/optimization with diverse accelerators.

- Co-scheduling Workloads with Near-data Processing.

- Multi-Tenant Support for colocating Diverse DL applications.

Eco-friendly DL with

Energy/Carbonaware HW-System

Co-Optimization

Dynamic Energy Scaling to balance runtime performance and energy cost.

Carbon-Aware Scheduling to balance energy availability and job requirements. Accelerated DL with

Reconfigurable

Dataflow Architecture

(e.g., SambaNova)

- Compiler optimization for dataflow design space search.

- Workload-aware Runtime Dataflow Reconfiguration.

#### Future Research: Exploring New DL Workloads

- Cross-iteration spatial and temporal in 360 Panorama rendering and 3D scene lifting.

- Cross device (e.g., multi-GPU platforms) objects artifacts locality.

#### Diffusion Model Serving

- SLO-aware dynamic repatching for efficient

- Patch-based early exit for efficient diffusion.

- Dynamic DL precision with multi-base LNS.

- Memory-efficient model quantization with selective LNS.

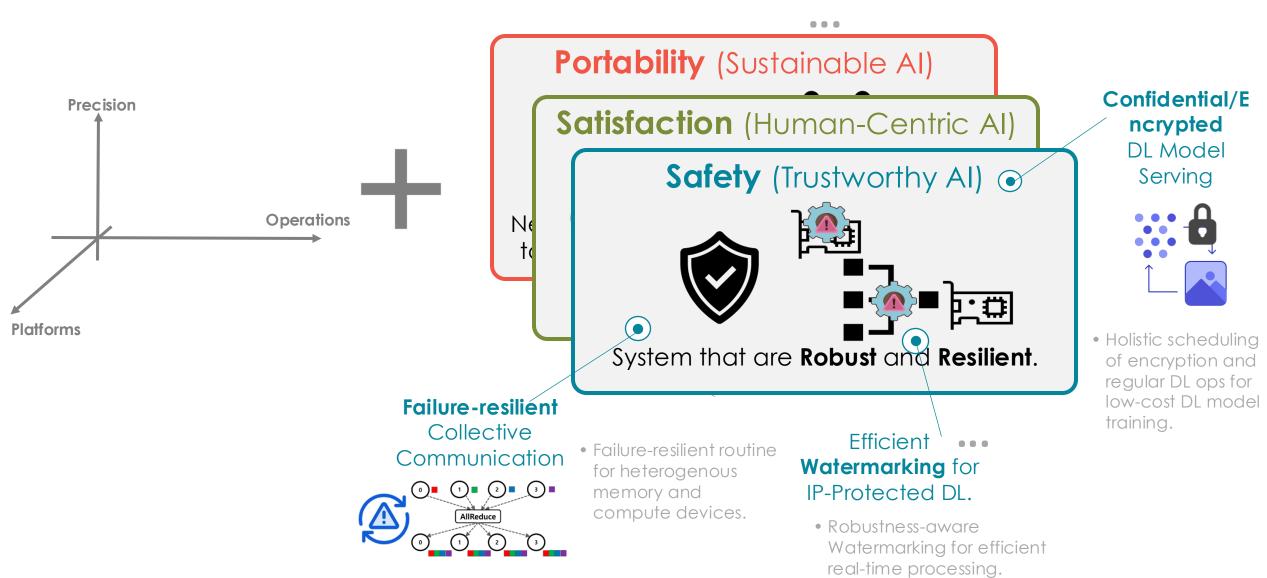

#### Future Future: Secure and Resilient DL System

### Thank You

Q & A

GitHub github.com/YukeWang96